关键词:延时;并网变流器;稳定性;数字信号处理器

1 引言

相比模拟控制,数字控制具有噪声容限大、抗干扰能力强、易于实现复杂算法、可重复编程等优点[1]。而数字控制系统A/D转换环节、计算环节、PWM加载环节等都可能会引起控制延时,控制延时的引入相当于在控制系统的前向通道串入延时环节,对数字控制系统的性能有很大的影响。由于延时,系统的带宽被减小,甚至发生振荡进入不稳定的状态。

本文以单电感滤波的二极管钳位三电平并网变流器为例,首先介绍其典型的拓扑结构和控制原理,在此基础上分析几种典型数字控制系统软件架构下控制延时的区别,并在Matlab中仿真验证不同延时对控制性能的影响。提出一种工程上基于DSP数字控制系统的缩短控制延时的方法,在不增加系统硬件成本的情况下尽量缩短控制延时,用于提高控制性能和改善稳定性。样机的试验结果验证了方法了有效性。

2 并网变流器典型控制系统延时及影响

2.1 拓扑结构和控制原理

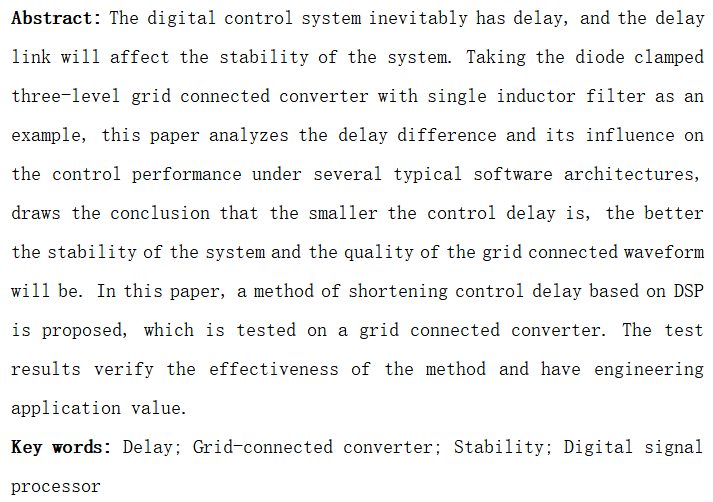

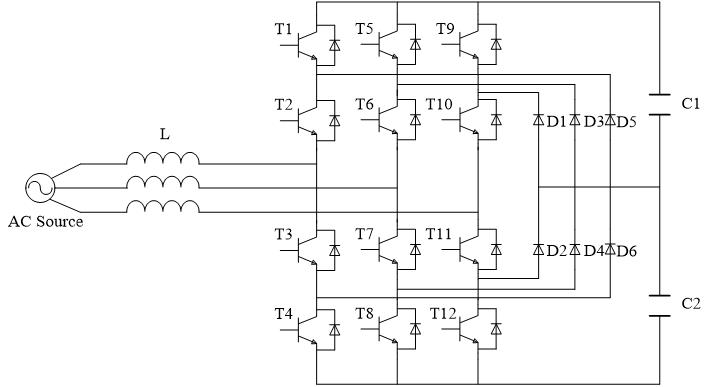

二极管钳位三电平并网变流器的典型拓扑如图1所示,控制上一般采用电压外环、电流内环的双闭环控制,其控制原理如图2所示。通过电压、电流的park变换将三相静止矢量变换为d、q轴两相同步旋转矢量,在d、q轴进行电流闭环控制,达到反馈跟踪指令的目的,同时通过前馈解耦的方式实现有功无功的解耦控制[2]。

图1 二极管钳位三电平并网变流器拓扑结构

图2 双闭环控制原理

2.2 常规的数字控制延时

一般的数字控制系统软件架构有以下几种方式:

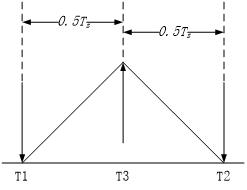

方式一:控制软件设置一个载波下溢中断(载波波谷),加载方式为下溢加载。在载波下溢中断中进行A/D采样、调制度计算等核心算法处理,这样计算出的调制度只能在下一个载波周期的下溢时刻使用,数字控制引起的延时为一个载波周期Ts。如图3(a)所示,在T1时刻开始核心算法计算并得到调制度,在T2时刻加载使用。方式二:控制软件设置周期中断(载波波峰)和下溢中断(载波波谷)两个中断,加载方式为波峰波谷加载。在两个中断中均进行核心算法计算并得到调制度,如图3(b)所示,T1时刻计算得到的调制度在T3时刻加载使用,T3时刻计算的调制度在T2时刻加载使用,这样数字控制引起的延时始终为0.5倍的载波周期,即0.5Ts。

(a)

(b)

图3 常规软件架构控制延时

2.3 缩短控制延时的方法

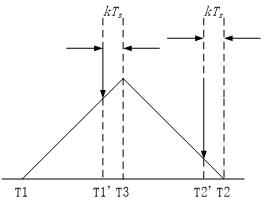

2.2小节所述的控制系统引起的控制延时为一个载波周期或半个载波周期,为了进一步缩短控制延时,提高系统的稳定裕度,增大系统的带宽,改善并网性能指标,提出图4所示的延时控制方法。在波峰T3前的T1′时刻进行A/D采样和核心算法处理并得到调制度,在T3时刻加载使用。同样地,在波谷T2前的T2′时刻进行AD采样和核心算法处理并得到调制度,在T2时刻加载使用。控制T1′至T3,T2′至T2的时间均为kTs。而kTs的大小取决于数字控制器A/D采样和相关的控制代码执行的时间,对于目前主流的数字信号控制器,尤其是开关频率相对较低的场合,很容易实现k<<0.5。

图4 缩短控制延时的方法

2.4 仿真验证

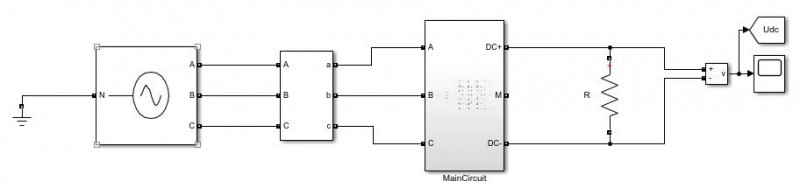

在Matlab/Simulink中搭建二极管钳位三电平并网变流器的仿真模型,主回路的仿真模型如图5(a)所示,控制系统的仿真模型如图5(b)所示。仿真参数如下:电网线电压1000V,滤波电抗电感量L=2mH,直流电压目标值1800V,直流侧负载电阻R=20![]() ,载波频率为5kHz,调制方式为载波同相层叠。

,载波频率为5kHz,调制方式为载波同相层叠。

(a)主回路模型

(b)控制系统模型

图5 仿真模型

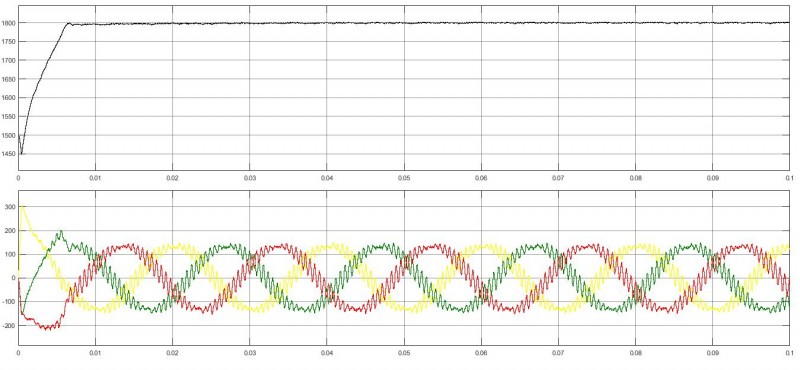

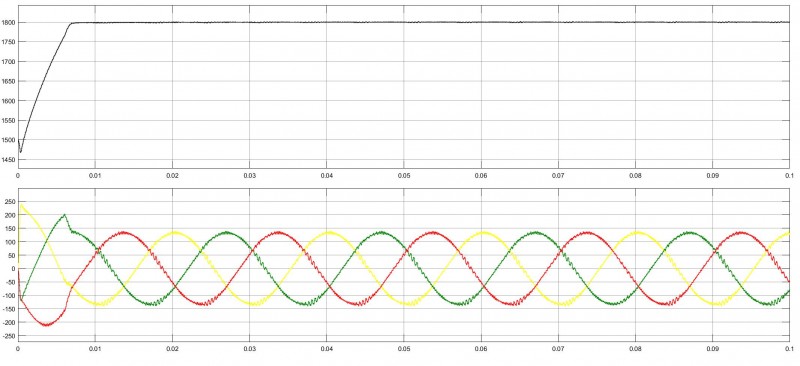

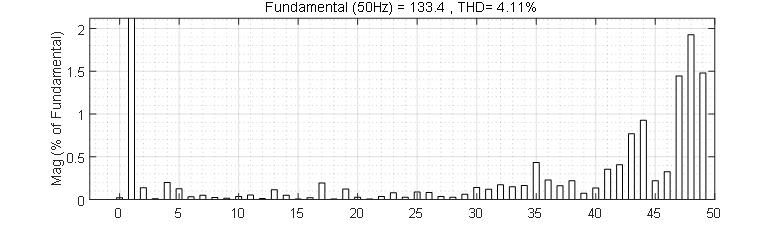

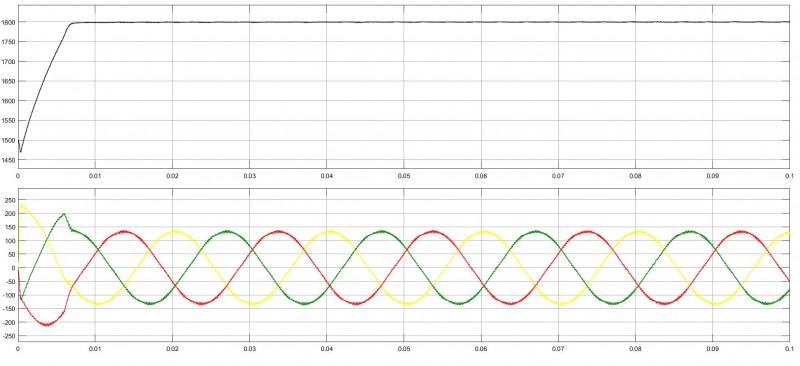

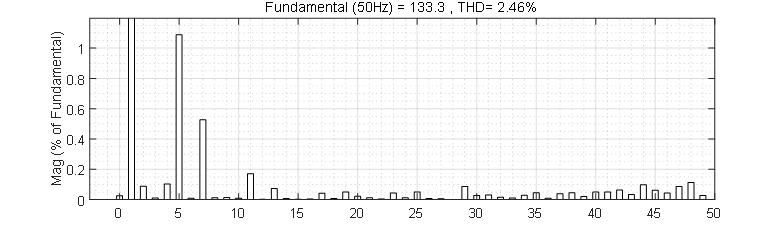

图6中的(a)(c)(e)分别对应控制延时为Ts、0.5Ts、kTs(k=0.1)的直流电压和并网电流波形,(a)图显示在控制延时为Ts时并网电流出现了一定振荡,(c)图显示控制延时为0.5Ts时并网电流的稳定性有很好的改善;(e)图显示控制延时为0.1Ts时并网电流的稳定性最好,波形质量最好。(b)(d)(f)分别对应控制延时为Ts、0.5Ts、kTs(k=0.1)的并网电流的谐波大小,分别为21.11%、4.11%、2.46%。从仿真结果看,缩短控制延时对提高控制系统的稳定性、并网波形质量都有一定的好处,同时也验证了2.3小节提出的缩短控制延时的方法是可行的。

(a)

(b)

(c)

(d)

(e)

(f)

图6 仿真结果

3 基于DSP的缩短控制延时的实现方法

以TI公司的TMS320F28335 DSP芯片为例说明实现缩短控制延时的方法。基本思想如下:程序设置一个A/D中断,波峰波谷均加载方式。在载波波峰前和载波波谷前的合适时刻产生SOC信号(ADC启动转换信号),转换完成后会进入A/D中断,在中断中利用最新的A/D采样值进行核心算法处理,得到ePWM的比较值并加载到CMP比较寄存器中。上述所有动作要在波峰或波谷时刻到来之前完成,在波峰、波谷到来时刻恰好利用刚计算的比较值进行加载。

图7 基于DSP的缩短控制延时方法示意图

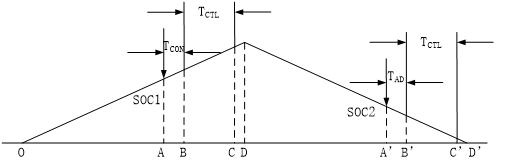

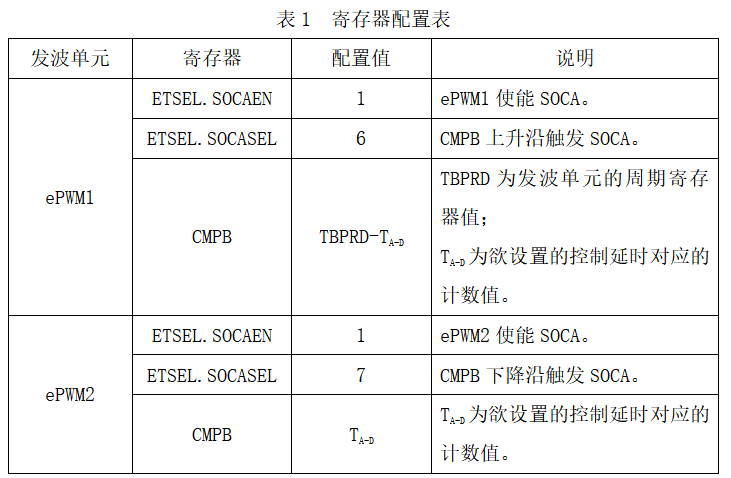

如图7所示,OD′为一个载波周期,在载波的上升沿A时刻和下降沿A′时刻产生SOC1和SOC2信号,触发A/D转换,转换结束后产生A/D中断,即在B和B′时刻进入A/D中断。由SOC产生至进入A/D中断即A/D转换所需要的时间为TCON。进入A/D中断后,开始进行控制相关的代码处理,在C和C′时刻得到比较值并加载至CMP,由B至C就是控制相关代码的执行时间为TCTL。在D和D′时刻真正使用CMP中的比较值。A时刻至D时刻或A′时刻至D′时刻之间的时间TA-D、TA’-D’就是数字控制系统总的延时时间,该时间的大小取决于A/D采样时间和必要的控制代码的执行时间之和。通过对DSP相关寄存器的配置即可实现上述控制延时的方法,DSP相关寄存器的配置如表1所示[3]。

4 试验结果

为了验证本文分析的正确性,搭建试验样机,控制器为DSP28335。试验参数如下:电网电压1140V,载波频率5kHz,并网电抗1mH,直流电压目标值1830V。

采用图3(b)软件架构,控制延时0.5Ts下的并网电流波形如图8(a)所示,采用图7所示的缩短控制延时的方法,控制延时为0.1Ts,并网电流波形如图8(b)所示。同样的试验条件和控制参数,图8(a)并网电流出现了一定的低频振荡,而图8(b)并网电流波形稳定且正弦度较好。试验结果证明本文所提的缩短延时的方法有利于提高并网变流器控制系统的稳定性并改善并网电流波形质量。

(a)0.5Ts延时并网电流波形 (b)0.1Ts延时并网电流波形

图8 不同延时下的并网电流波形

5 结论

数字控制中的延时是不可避免的,一般的控制延时为一个载波周期或半个载波周期,当开关频率较低时,即使半个载波周期的延时对系统的控制性能也有较大的影响。本文以单电感滤波的二极管钳位三电平并网变流器为例,分析几种典型数字控制系统软件架构下控制延时的区别,并在Matlab中仿真验证不同延时对控制性能的影响。提出一种工程上基于DSP数字控制系统的缩短控制延时的方法,在不增加系统硬件成本的情况下尽量缩短控制延时,用于提高控制性能和改善稳定性。样机的试验结果验证了方法的有效性,具有工程应用价值。

共0条 [查看全部] 网友评论