关键字:碳化硅;并联;双脉冲测试

Abstract: There are 4 pcs 6mohm SiC module paralleling with symmetrical layout design and the test result is given. Finally, a Monte Carlo analysis is used to demonstrate the effects on the temperature sharing due to production spreads in device parameters. So, it is possible to do SiC module paralleling.

Keywords: SiC; Paralleling; Double pulse test

1 引言

用硅IGBT的工程师们很多曾经有过并联器件的使用经历,它不仅能降低成本还能减小整体系统分布电感。那么对于新一代的半导体器件SiC而言,是否一样可以并联使用呢?以下就以4个英飞凌6mohm的SiC模块的硬并联为例,来一起看看实现的可行性。

2 四个并联模块分析

2.1 均流类型

任何的同一料号开关器件并联,均流总是最重要的目的,这关系到整个系统的最终功率等级,所以如何做到均流就会是一个挑战。一般我们会按动态均流和静态均流分别讨论它。动态均流和系统设计有很大的关系,包括门极驱动、母排结构、PCB布线,甚至功率器件和负载摆放的位置都会影响均流效果。而静态均流和器件本身以及结构的几何形态关系密切,得益于如今市场上大部分的功率半导体是正温度系数的,所以静态均流比较容易实现,对器件批次的参数差异要求不多,文章最后会给出蒙特卡洛分析来评估。

2.2 整体结构

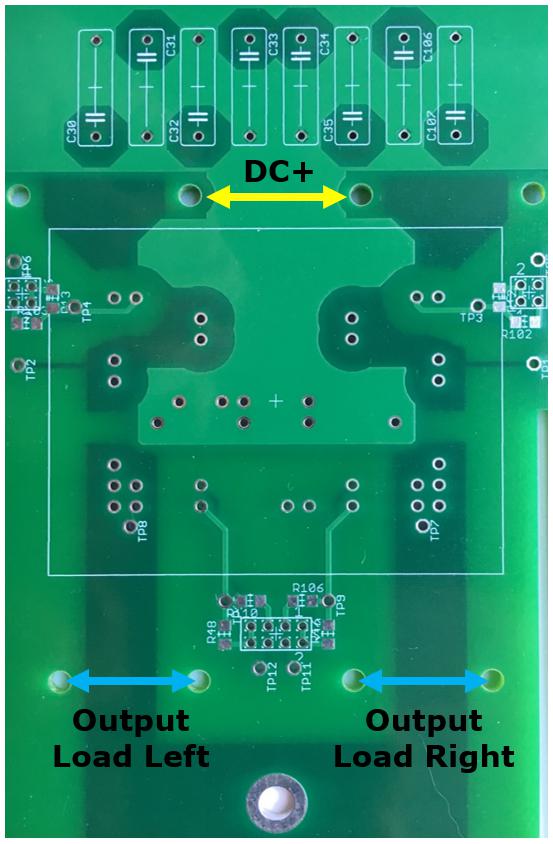

首先我们来讨论一下整体结构。由于要实现最小的电流回路,整个系统做成了分开的主功率板和驱动电路板,用接插针来连结两块板子,如图1所示。这样的好处是4路驱动到4个并联模块的距离相等。再来看一下主功率板的布局如图2。用多层PCB来实现多层母线的结构,这样的杂散电感很小,每路只有大约19nH,4个并联后总的杂散电感不超过5nH。可以看到整个主功率板超级对称,这对并联应用是最重要的,没有之一。如果看不清楚,没关系,请参考图3单路的高清放大图,上排的孔是用来套超细柔性探头测桥臂电流;下排的孔是留来测负载电流的。这些孔在实验阶段很好用,当然在正式的设备量产板上是要去掉的,去掉后母排叠层区域面积变大,系统的杂散电感会进一步减小的。

图3 单个主回路

2.3 四并联驱动

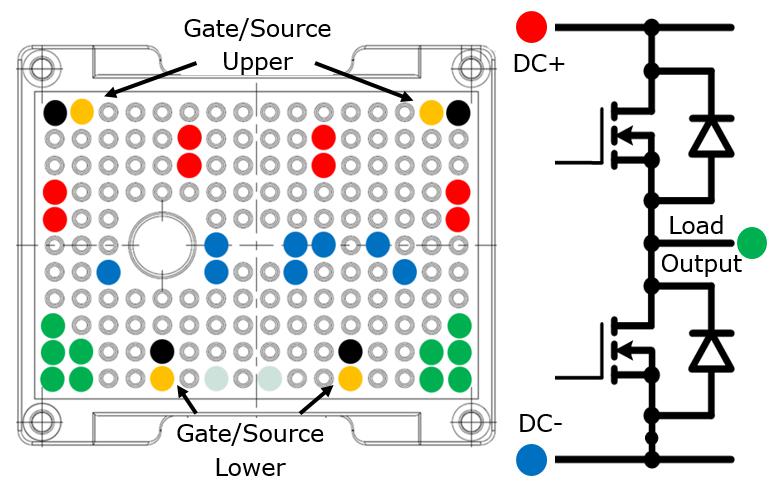

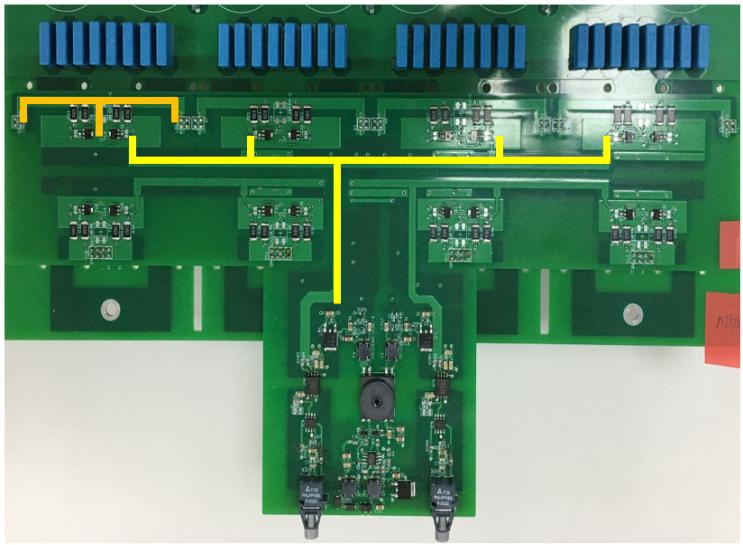

我们再来看一下这个4并联的驱动。图4是这个模块的管脚布局图,这个模块的上下桥模块每个都拥有两路gate,两路source,且他们在模块内部是电气相连的。这样做不仅可以减小门极的寄生电感,还能改善模块内部SiC芯片的电流分布。鉴于这样的模块门极结构,外围的驱动电路也应做到与之相配,也就是说接到两个G、S也要对称,以保证左右两边的开关时间高度一直。可以用图5这样的树形结构,橘黄色是到左右两边的驱动信号,黄色是驱动板至4路SiC模块的驱动信号。经实测,4并联8组驱动信号之间的延时误差不超过5ns。

图4 模块管脚布局

图5 门极驱动的树形结构

2.4 测试结果

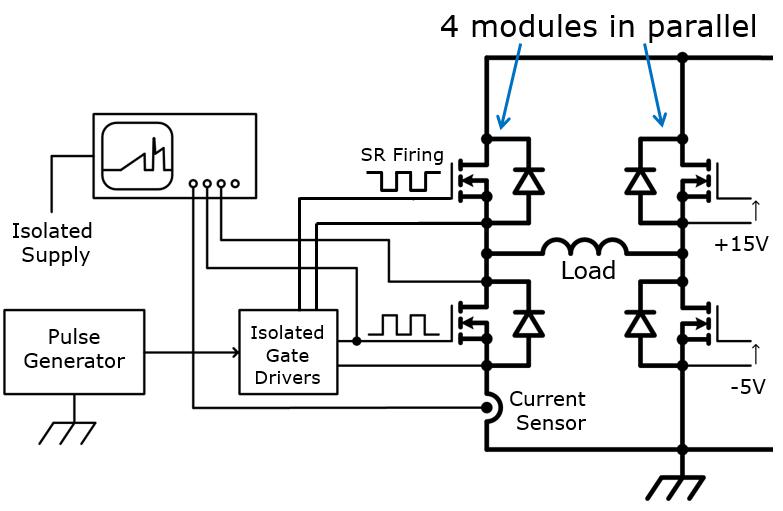

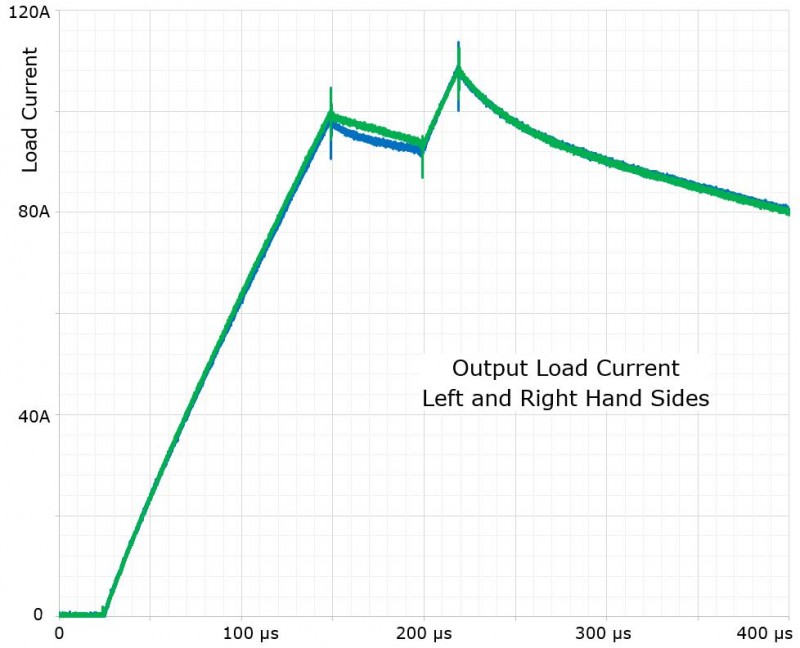

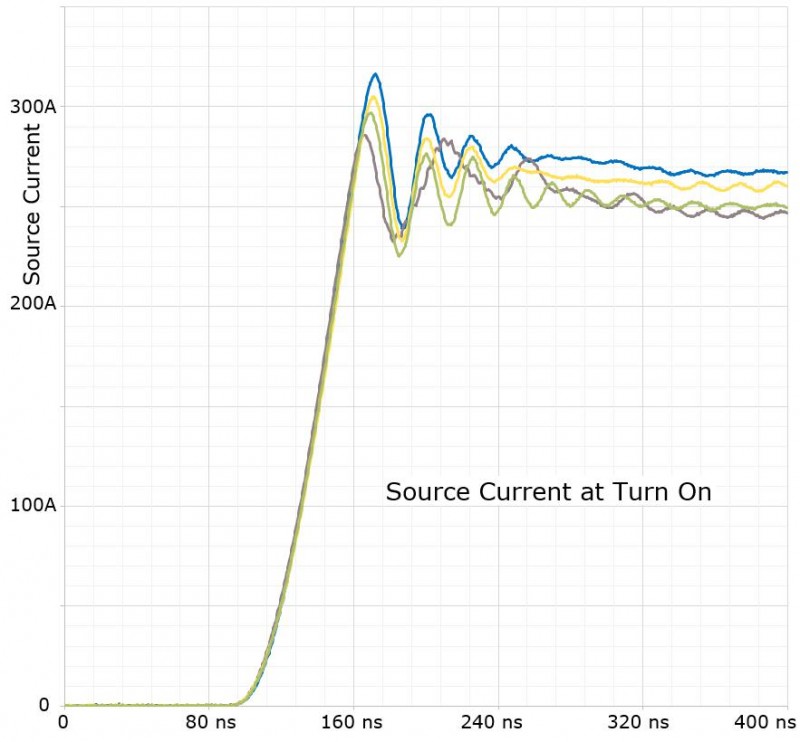

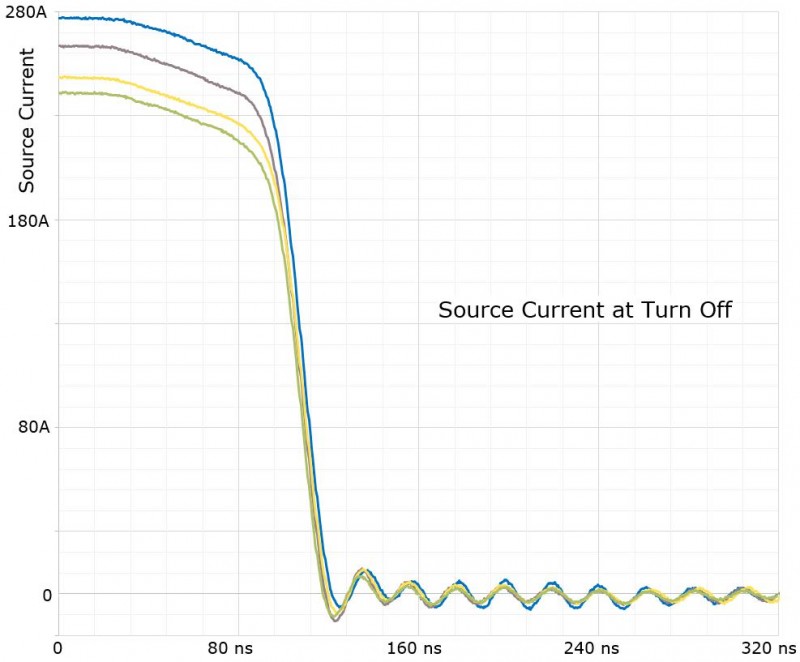

这么对称的母排和驱动,实际测量中均流到底好不好呢?接下来,让我们一起见证一下结果。需要说明的是测试所用的双脉冲测试电路结构是全桥的,并非常规用的半桥模式,原理如图6。如此做的好处是可以减小半桥测试时负载电感对回路的电磁场影响。各个器件的门极信号给定也在图中有显示。由于SiC器件的体二极管导通压降大且偏差也大,所以在续流是可以使用同步整流模式,但要留出一定的死区时间,对SiC器件而言一般不超过1μs。图7是单个模块左右两侧的负载电流,可以看出两者的均流度非常好。我们不仅要对每个模块的左右电流均流度进行确认,还要对不同模块同一侧电流进行比较,这样能保证器件并联后达到最大的输出电流。图8和图9分别是4个并联模块的开通和关断电流,上升和下降的斜率一致性非常高,而且没有什么振荡。改变温度,母线电压和门极电阻后,均流的趋势几乎是一样的。

图6 全桥双脉冲测试

图7 单个模块左右两侧的负载电流

图8 开通电流

图9 关断电流

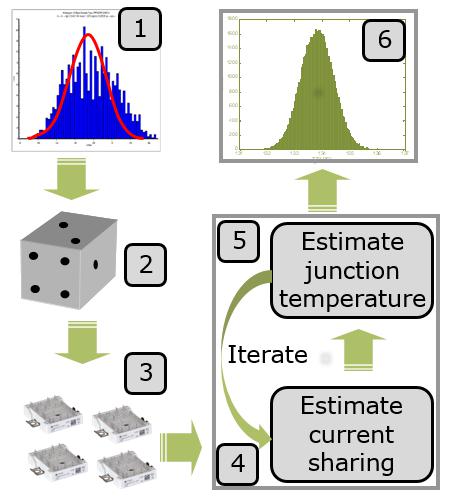

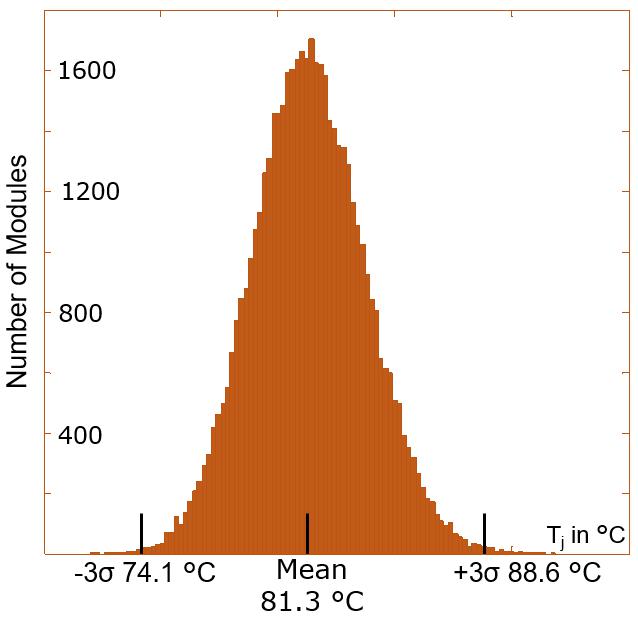

以上的这些测试结果都是针对数量有限的模块的,那么对于批量的产品而言,均流又怎样呢?最后,给出了蒙特卡洛来进行热分析。这个理论简单地说就是反复地随机取样,以得到最终事件概率。图10所示,用在本次模块并联分析中就是从一个50000个不同损耗的样本库中,随机抽出4个进行组合,然后进行电流与温度的迭代,获得该组并联时的温度差。多次重复进行这样的随机抽取,把所有的温度差按出现的次数绘成柱状图就是图11。

图10 蒙特卡洛过程

图11 并联温度偏差

3 结束语

SiC器件的并联肯定是可行的,但最最关键的一个词就是“对称”。“对称”能从根本上解决各类振荡和不均流问题。另外,使用同步整流还有助于续流时的均流,特别对二极管损耗占比偏高的应用大益。

参考资料:

[1]Infineon AN 2017-41. Evaluation Board for CoolSiC™ Easy1B half-bridge modules[Z].

[2]Infineon AN 2017-04. Advanced Gate Drive Options for Silicon- Carbide (SiC) MOSFETs using EiceDRIVER™[Z].

[3]Infineon AN2014-12. EiceDRIVER™ 1EDI Compact Family. Technical description[Z].

[4]Infineon AN2018-09. Guidelines for CoolSiC™ MOSFET gate drive voltage window[Z].

[5]Infineon AN2017-14. Evaluation Board EVAL-1EDI20H12AH-SIC[Z].

[6]Infineon AN2007-04. How to calculate and minimize the dead time requirement for IGBT’s properly[Z].

[7]Infineon AN2017-46. CoolSiC™ 1200 V SiC MOSFET Application Note[Z].

共0条 [查看全部] 网友评论