关键词:IEC60044-8;FPGA;MATLAB;任意多项式CRC

Abstract: With the continuous development of electric power technology, the demand for the coordinated control of multiple sets of dynamic reactive power compensation devices is increasing, and the coordinated control based on the IEC60044-8 protocol of Manchester code is applied. To ensure the reliable transmission of power communication system data, a parallel CRC logic circuit is designed on the basis of the FT3 format and implemented on the FPGA. On this basis, through MATLAB and FPGA, the implementation of arbitrary M*N polynomial CRC is extended. The simulation and experimental results show that the IEC60044-8 parallel CRC logic circuit implemented by FPGA has high real-time performance, fully utilizes the advantages of FPGA's parallel processing, can be easily applied to power communication systems, and has extensive popularization value.

Keywords: IEC60044-8; FPGA; MATLAB; Arbitrary Polynomial CRC

1 引言

近年来,随着我国经济的迅速发展,对电力的需求日益增大。电力系统的电压等级和容量方面日益增加,同一新能源场站的多套动态无功补偿装置(SVG)需求越来越多,多套动态无功补偿装置间协调控制以及与变电站自动化系统的接口与通信,对于变电站的数字化有着重要的意义。为了保证变电站整个通信系统点对点链接的兼容性,从而满足所有各类设备装置之间的信息交换。这些内容建立了点对点串行链接的布局,允许不同制造厂的设备可以交互使用。

2 IEC 60044-8协议

2.1 物理层规则

多套SVG之间设备的联结,可用光纤传输系统实现,高位定义为“光线亮”,低位定义为“光线灭”。通用帧的传输速度为10Mbit/s。采用的Manchester编码:规定曼彻斯特编码时从低位转移到高位为二进制1,从高位转移到低位为二进制0。

2.2 链路层规则

链接层选定为IEC 60870-5-1的FT3格式。此格式的数据编码具有良好的数据完整性,且其帧结构使它有可能用于高速度的多点网络同步数据链接。

FT3帧数据传输规则规格如下:

(1)行空位是二进制1。两帧之间按Manchester编码连续传输此值1,为了使接收器的时钟容易同步,由此提高通讯链接的可靠性。两帧之间应传输最少20个空位毕特。

(2)帧的最初两个八位字节代表起始符。

(3)16个八位字节用户数据由一个16毕特校验序列结束。需要时,帧应填满缓冲字节,以完成给定的字节数。

(4)校验序列建立一个多项式生成码:X16 + X13 + X12 + X11 + X10 + X8 + X6 + X5+ X2 + 1。此规范生成的16比特校验序列需按位取反。

(5)接收器检验信号品质、起始符、各校验序列和帧长度。如果这些检验中任一项有误,该帧将废弃,否则交付给用户[1]。

3 循环冗余校验

为了确保数据的可靠传输,需要在数据链路中加入差错检测码。CRC码是在严密的代数学理论基础上建立的,以其实现简单,抗干扰能力强而得到广泛应用,IEC 600448-8标准中便是使用CRC校验码进行差错检测和控制的。采用CRC校验时,发送方和接收方预先约定一个生成多项式G(x),该生成多项式作为除数多项式IEC60044-8中所规定的生成多项式![]() ,将要发送的数据比特序列作为一个多项式F(x)的系数,该多项式为被除多项式,用G(x)除F(x)得到一个余数多项式,该余数多项式的系数即构成了数据比特序列的CRC校验码,将它添加到数据序列之后一起发送到接收方。接收方同样将接收到的数据看成是一个多项式的系数,并用相同的生成多项式除该多项式,若得到的余数为0,表示传输过程无差错,否则表示出错[2]。

,将要发送的数据比特序列作为一个多项式F(x)的系数,该多项式为被除多项式,用G(x)除F(x)得到一个余数多项式,该余数多项式的系数即构成了数据比特序列的CRC校验码,将它添加到数据序列之后一起发送到接收方。接收方同样将接收到的数据看成是一个多项式的系数,并用相同的生成多项式除该多项式,若得到的余数为0,表示传输过程无差错,否则表示出错[2]。

发送方编码过程如下:首先,将待发送数据多项式F(x)乘以![]() ,其中k为生成多项式

,其中k为生成多项式

G (x)的最高幂次,对于二进制乘法,首先将对应的发送比特序列左移16位。其次,用G(x)去除以上的乘积,可得结果为Q (x) + R(x)/G (x),式中Q (x)为商,R(x)为余数多项式。令![]() 将M (x)所对应的比特序列作为一个整体发送。

将M (x)所对应的比特序列作为一个整体发送。

接收方校验时,对接收序列所对应的多项式M′(x)作如下处理:计算M′(x)/G(x),若M′(x)/G (x) = Q (x),余数为0,则M′(x) =M (x),认为传输正确;若M′(x) /G (x)余数不为 0,则认为传输有错。

在实际应用中,CRC的校验值计算分两种:传统的按位计算和并行处理算法,其中按位算法无法满足现有高速链路的需求,目前基于矩阵处理的并行CRC硬件电路得到广泛采用。由于FPGA的并行处理算法,可以不需要查表直接通过Scramble (CN)网络来实现[3]。

4 并行CRC的设计与实现

首先定义方程变量:需要处理n+1位数据,生成多项式的最高次幂为m(长度为m+1),校验序列长度为m,并行处理长度为w。

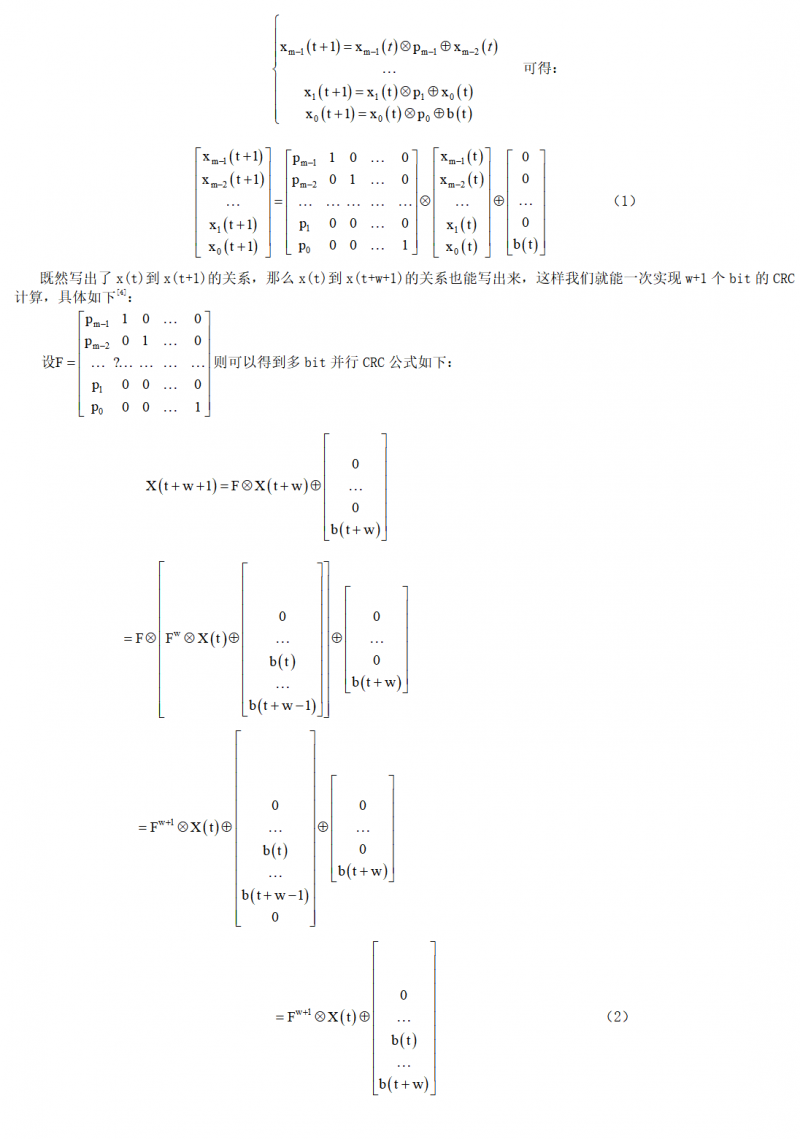

从单bit实现入手,从x(t)到x(t+1),(x0, x1, …, xm-1)是当前要与被除数poly: (p0, p1, …, pm-1, pm)相异或的数据,b(t)是刚进入的新的bit。(![]() )

)

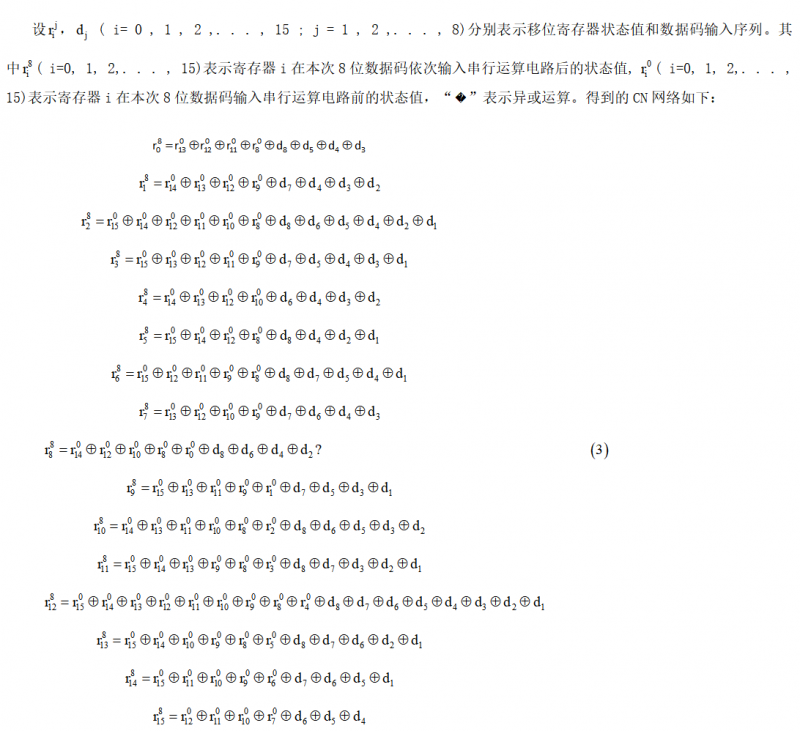

在Matlab和Modelsim中对上述CN组合网络进行联合仿真,模拟输入16个字节{0x11 0x12 0x13 0x14 0x15 0x 6 0x17 0x18 0x19 0x20 0x21 0x22 0x23 0x24 0x25 0x26},依次输入并行数据,8位并行数据码与寄存器初始值按照前面推导出的逻辑关系进行异或运算,所得16位CRC余数值存入寄存器,供下次并行运算使用。当下一个字节数据来临时,再将这个数据与寄存器当前的余数值进行异或运算,所得新余数存入寄存器。依此类推,当16个字节的数据码全部输入完毕,生成的校验码为1F4AH,这与串行编码的结果保持一致。并行CRC编码结果及串行编码的结果如图1所示。

图1 并行CRC编码结果及串行编码的结果

5 FPGA实现任意多项式CRC

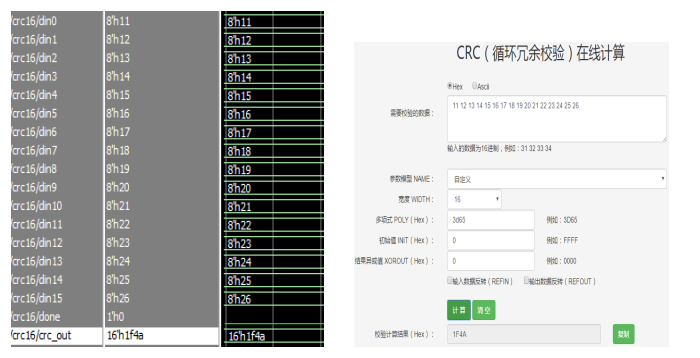

如图2所示,CN为FPGA实现的生成多项式组合逻辑,DFF(M)为中间变量寄存器,代表M个校验位,Data[N-1:0]代表输入为N位。

图2 任意多项式CRC结构框图

对输入的数据进行提前抽取,通过关系函数得到下一个clock寄存器的输入nxt_crc[M-1:0]:关系函数CN为:nxt_crc=CN(crc_out,data),crc_out是前一个clock的寄存器输出;data是当前的输入数据;函数CN就是一个组合逻辑网络。

以M=16,N=16的CRC16-16(poly:0x8005)为例,生成多项式取x^16+x^15+x^2+1,初始值为全0;首先根据行列式得到每个bit的CN的逻辑网络,并行poly为8005,800f,801b,8033,8063,80c3,8183,8303,8603,8c03,9803,b003,e003,4003,8006,8009。

将上面的并行poly转化为如下的CN网络组合逻辑:

newcrc[0] =

d[0]^d[1]^d[2]^d[3]^d[4]^d[5]^d[6]^d[7]^d[8]^d[9]^d[10]^d[11]^d[12]^d[13]^d[15]^

c[0]^c[1]^c[2]^c[3]^c[4]^c[5]^c[6]^c[7]^c[8]^c[9]^c[10]^c[11]^c[12]^c[13]^c[15];

newcrc[1] =

d[1]^d[2]^d[3]^d[4]^d[5]^d[6]^d[7]^d[8]^d[9]^d[10]^d[11]^d[12]^d[13]^d[14]^

c[1]^c[2]^c[3]^c[4]^c[5]^c[6]^c[7]^c[8]^c[9]^c[10]^c[11]^c[12]^c[13]^c[14];

newcrc[ 2] = d[0]^d[1]^d[14]^c[0]^c[1]^c[14];

newcrc[ 3] = d[1]^d[2]^d[15]^c[1]^c[2]^c[15];

newcrc[ 4] = d[2]^d[3]^c[2]^c[3];

newcrc[ 5] = d[3]^d[4]^c[3]^c[4];

newcrc[ 6] = d[4]^d[5]^c[4]^c[5];

newcrc[ 7] = d[5]^d[6]^c[5]^c[6];

newcrc[ 8] = d[6]^d[7]^c[6]^c[7];

newcrc[ 9] = d[7]^d[8]^c[7]^c[8];

newcrc[10] = d[8]^d[9]^c[8]^c[9];

newcrc[11] = d[9]^d[10]^c[9]^c[10];

newcrc[12] = d[10]^d[11]^c[10]^c[11];

newcrc[13] = d[11]^d[12]^c[11]^c[12];

newcrc[14] = d[12]^d[13]^c[12]^c[13];

newcrc[15] =

d[0]^d[1]^d[2]^d[3]^d[4]^d[5]^d[6]^d[7]^d[8]^d[9]^d[10]^d[11]^d[12]^d[14]^d[15]^

c[0]^c[1]^c[2]^c[3]^c[4]^c[5]^c[6]^c[7]^c[8]^c[9]^c[10]^c[11]^c[12]^c[14]^c[15];

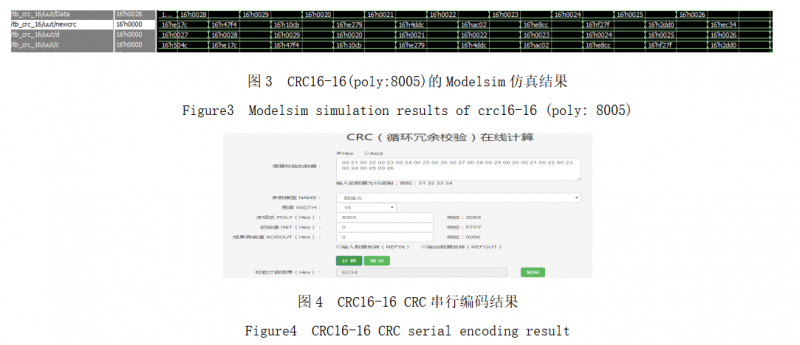

CRC16经过计算得到EC34H,和CRC串行在线计算工具得到的结果是相同的。证明只要提供合适的组合逻辑就可以完成任意设定位宽的任意多项式的CRC计算,充分利用FPGA的并行处理能力,具有很高的应用价值。CRC16-16(poly:8005)的Modelsim仿真结果如图3所示。CRC16-16 CRC串行编码结果如图4所示。

6 结束语

按照IEC 60044-8标准的要求,本文设计了多套动态无功补偿装置(SVG)协调控制, 重点研究了结合标准FT3所规定的CRC生成多项式, 在串行设计基础上,给出了详细的并行推导过程,通过FPGA并行实现,具有很高的实时性,实践证明完全是可行的。通过Matlab和Modelsim完成了FPGA任意阶次及任意位宽的生成矩阵的推导,并行处理带宽的增加能够有效地提高CRC处理速度,可方便地应用于电力通信系统,具有广泛的推广应用价值。

参考文献:

[1] International Electrotechnical Commission. IEC 60044-8 Instrument transformers part8: electronic current transducers[S]. IEC,2002.

[2]朱雷,郑绳楦. IEC60044-8标准中CRC校验码的硬件实现[J]. 自动化仪表, 2006,27(03):18-21.

[3]李伟,尹项根,韩小涛. 基于IEC60044 -7/8的光电式互感器在变电站自动化系统中的应用[J]. 电力自动化设备, 2003,23 (05):39-42.

[4]梁海华,盘丽娜,赵秀兰,李克清. CRC查询表及其并行矩阵生成方法[J]. 计算机科学, 2012,39(06):152-158.

[5]薛俊,段发阶,蒋佳佳,李彦超,袁建富,王宪全. 基于Matlab的并行循环冗余校验Verilog代码自动生成方法[J]. 计算机应用, 2016,36(09): 2503:2507,2554.

[6]阚佳冲,潘文明,郑坚泽,潘全. 基于FPGA全参数化CRC的推导及实现[J]. 现代电子技术, 2015,38(08):154-158.

作者简介:

赵爽 出生日期:19840601,性别:男 ;学位:硕士;单位:荣信股份;研究方向:谐波治理及无功补偿

共0条 [查看全部] 网友评论