赵爽,孙贤大,祝贺,苏建

(辽宁荣信电力电子技术有限公司,辽宁 鞍山 114000)

关键词: FPGA;LIUNX;OPENAMP; FMC

中图分类号:761 文章标识码:A 文章编号

High-speed communication implementation based on

STM32MP1 heterogeneous multi-core and FPGA

Zhao Shuang,Sun Xianda,Zhu He,Su Jian

(Liaoning Rongxin Power Electronic Co.,Ltd.,,Anshan 11400, China)

Abstract: In the power electronic system, the signal and processing real-time and throughput demand for the power grid is increasing, STMicroelectronics STM32MP1 series embedded system LIUNX chip internal integration of heterogeneous core architecture Cortex-A7 and Cortex-M4 in its shared memory through the Open Accelerated Massive Parallelism(OPENAMP) protocol to complete the inter-core communication. INTEL's ALTERA series of Field-Programmable Gate Array (FPGA) for parallel architecture processing chip, can simultaneously process information from multiple electronic devices, including power grid, load, compensation equipment voltage and current information. It can simultaneously process information from multiple electronic devices, including voltage and current information of power grid, load, and compensation equipment.The Flexible Memory Controller (FMC) bus is used for high-speed communication between LIUNX and FPGA, and the maximum data processing space of 25-bit address and 16-data can be accomplished. Experiments have shown that data communication acquisition can be accomplished through coordinated cooperation with high interaction rate and high throughput, which greatly improves the performance of power electronic equipment.

Keywords: FPGA;LIUNX;OPENAMP; FMC

1 引言

在电力电子系统中,需要对电网,负载,及补偿设备的电压,电流,相位,频率等信息进行监测。传统的多通道数据采集系统大多采用两种方式,其中一种采用数据采集卡的方法,但其设计核心技术不公开,无法针对具体需求修改和升级,而且集成度不高,价格昂贵,后期维护不便[1]。另外一种采用模数转换(Analog to Digital Converter, ADC)芯片的多通道分时复用实现,此方法难以实现同步和高速高精度采集[2]。

在实际电力电子运行中,以往都是设备通过DSP和FPGA进行设备级的数据处理,当数据量很大时,需要linux系统对多台设备通过61850或者IEC104等复杂协议的进行用统一的协调处理。

意法半导体(STMicroelectronic,ST)推出的 STM32MP1系列芯片有Cortex-A7 内核和Cortex-M4 内核,它属于异核异构,其中Cortex-A7 内核可以运行 Linux 操作系统[3], Cortex-M4 内核以运行实时程序或者实时操作系统[4] (Real Time Operating System, RTOS)。A7核和M4核之间采用OPENAMP通信。

INTEL公司的ALTERA系列FPGA 芯片资源丰富,提供各种可配置的嵌入式(Static Random Access Memory,SRAM)、高速收发器、高速 I/O、逻辑模块和路由。根据需求FPGA 功能可以更改内部电路程序。加快产品上市速度和/或提升系统性能。Linux和FPGA之间采用FMC总线[5]通信。

FMC支持不同位宽的异步读写操作,FMC配置的地址线,数据线和控制线是共享的) ;每个片选下的存储器空间配置都是独立的,有专门的寄存器,互不影响。使用FMC,可以用来驱动FPGA,AD7606,OLED,DM9000等各式并行控制设备。

本文以 FPGA 和STM32MP1控制芯片为核心,设计(Open Asymmetric Multiprocessing, OPENAMP)通信和(Flexible Memory Controller,FMC)通信,测试性能并验证方案的可行性。

2 系统设计

本次设计LIUNX芯片使用的是 STM32MP151,STM32MP1系列封装是兼容的,可以根据需求将STM32MP151更换为STM32MP153或者STM32MP157获得更多的系统资源。

FPGA芯片使用的是EP4CGX50CF23I7,逻辑资源为49888,RAM资源为2562048bit, 内部有完整的时钟管理模块内嵌的底层功能单元和嵌入式专用硬核。

2.1 整体架构

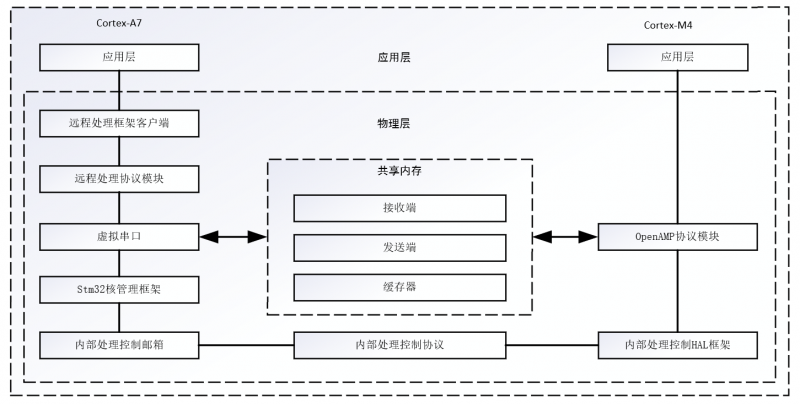

图1 整体框图

Fig. 1 Overall Block Diagram

如图1所示,左侧为LIUNX芯片,右侧为FPGA芯片,采用FMC总线进行通信。在LIUNX芯片内部,左侧为Coretx-A7,右侧为Coretx-M4,其内部包括DDR,SRAM和shared SRAM,A7独有外设和A7-M4共享外设,FMC接口, M4独有外设和A7-M4共享外设。Coretx-A7和Coretx-M4之间的SRAM存储空间通过共享RAM实现,外设通过通信总线连接。右侧的FPGA芯片内部,包括锁相环时钟,RAM存储资源,IP核模块及程序下载接口。

2.2 LIUNX异核框架

如图2所示, LIUNX中的Cortex-A7 和 Cortex-M4 内核之间分为应用层和物理层。在物理层中,Cortex-A7包括远程处理框架客户端和协议模块,虚拟缓存接口,内部处理控制邮箱, Cortex-M4包括内部处理框架和异核协议模块。

虚拟缓存接口和异核协议模块通过共享内存进行连接,共享内存包括接收端,发送端,和缓存器。其协议采用 (Inter-Processor Communication Controller,IPCC)协议连接,具体如下:当一个数据包被放入共享内存时,核1需要中断或“通知”核2有新的数据包在共享内存中要处理,核2收到信号后就去处理了,使用 IPCC 硬件中断机制来完成的。

图2 Cortex-A7和Cortex-M4连接框图

Fig. 2 Block Diagram of Cortex-A7

在中断机制中, Cortex-A7采用(Generic interrupt controller, GIC)中断, Cortex-M4采用 (Nested Vectoredinterrupt controller, NVIC)中断。 IPCC只是提供了处理器之间信息交换的机制,它并不具有数据传输功能,处理器之间要交互的数据是在共享内存中传输的。Cortex-A7中IPCC 处封装了邮箱(Mailbox)框架,邮箱框架主要用于通知共享内存中有数据要处理。

3 系统软件流程

3.1 LIUNX软件设计

根据不同的BOOT设置,分为工程模式和产品模式。工程模式中可以单独仿真Cortex-M4,产品模式需要首先启动Cortex-A7,然后引导加载Cortex-M4,这种模式是Cortex-A7跑的Linux系统从EMMC启动,然后加载Cortex-M4。

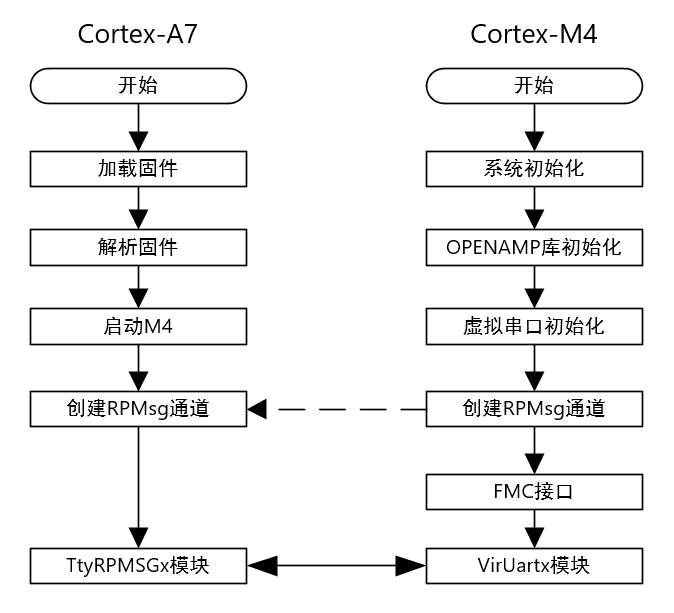

产品模式流程图如图3所示,左侧的Cortex-A7核上电后,加载程序所需的固件,在解析固件后启动Cortex-M4,创建(Remote Processor Messaging,RPMsg)通道。在同样的时间段内,右侧的Cortex-M4上电后进行系统初始化,OPENAMP库初始化,虚拟串口初始化,创建RPMsg通道。创建完之后,左侧的Cortex-A7通过创建ttyRPMSGx模块,右侧的Cortex-M4通过FMC写入和读取FPGA中的数据后,通过VirUart模块与ttyRPMSGx模块进行数据收发。

图3 软件设计流程图

Fig. 3 Software Design Flowchart

Cortex-M4软件流程如图4所示:上电后,M4核首先初始化系统时钟和外设资源,进而初始化IPCC和OPENAMP模块,然后初始化FMC接口和串口模块,进入主循环。在主循环中,当定时器中断置位后,通过FMC模块读取FPGA中的数据,校验正确后Cortex-M4向Cortex-A7发送数据,同时通过串口将数据显示出来。通过OPENAMP邮箱轮询来自Cortex-A7的数据,当接收到Cortex-A7数据后,通过FMC总线向FPGA更新数据,同时用串口显示更新的数据。

图4 Cortex-M4程序流程图

Fig. 4 Cortex-M4 program flowchart

3.2 FPGA软件设计

FPGA的设计流程包括设计定义、代码实现、功能仿真、逻辑综合、前仿真、布局布线、后仿真和板级调试等步骤。 Liunx芯片只需要经FMC总线下发控制命令,FPGA进行执行就可以了。

图5 FPGA程序模块

Fig. 5 FPGA Program Module

FPGA程序模块如图5所示,共分为三个模块,FMC_DECODE模块负责FMC总线通信,ADC_8555模块负责ADC数据采集,transceiver模块为高速光纤通信模块,负责和其它通信板卡交互数据。FPGA时钟部分采用50M晶振,负责各个模块的时序工作。另外FPGA还有1个相对于其它芯片的绝对优势,可以依据设计实际需要,在逻辑资源够的情况下,依据设计者来实现n个外设的例化。比如电力电子方面,FPGA例化多路电网波形通道配置,liunx对其下发命令,多个FPGA端电网电压电流采样及载波驱动可多通道同步执行。

3 实验验证与结果分析

3.1 Cortex-A7和Cortex-M4互传数据

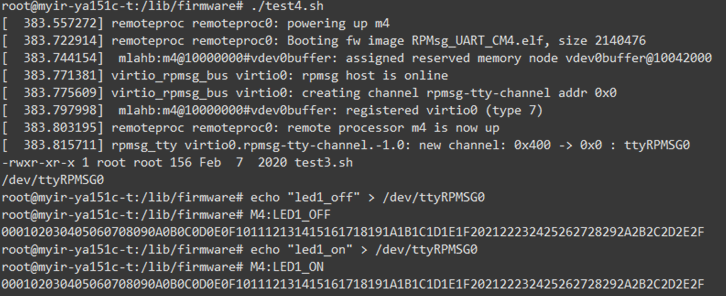

用网线连接板卡后,通过Xshell软件登陆板卡内LINUX系统,通过文本命令实现各项操作。

图6 liunx运行信息图

Fig. 6 The liunx runtime infographic

如图6所示,上电启动后,Cortex-A7通过指令启动Cortex-M4和ttyRPMSG0,启动成功提示remote processor m4 is now up。测试中,Cortex-A7核通过指令下发给Cortex-M4,Cortex-M4定时中断触发后,返回下发信息和需要上传的测试数据。

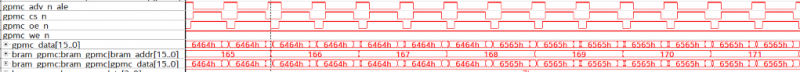

4.2 Cortex-M4和FPGA互传数据

FPGA板卡验证采用SignalTap实现,设置好采样的时钟、深度、要抓取的信号和触发条件,然后将综合后的程序下载到开发板中,最后在SignalTap II中观察波形。如图7(a)所示,在linux的写总线模式下通过gpmc_cs_n,gpmc_we_n将16位的数据通过bram_addr依次写入至gpmc_data中。如图7(b)所示,在linux的读总线模式下gpmc_cs_n,gpmc_oe_n,将16位的数据通过bram_addr依次从gpmc_data读出。

(a) 写GPMC总线

(b) 读GPMC总线

图7 FPGA在线仿真结果图

Fig. 7 FPGA online simulation result graph

4 结论

本文设计充分发挥异构多核STM32MP151中A7核系统框架优势和M4核中STM32实时处理器的运算能力,同时发挥FPGA的高速并行运行能力,通过FMC总线进行协调处理,通信速率可高达20M以上。对LIUNX芯片和FPGA芯片的通信接口提出比较好的通信拓扑,实际电网运行补偿或者出现故障时,linux 操作系统具有DSP不具备的系统级数据统计和波形处理,这对电力系统数据分析及并联补偿效果具有非常好的借鉴意义。

参考文献:

[1]王威,卢翔宇,张秋云,等.基于FPGA的便携式 多路高精度采集系统设计[J].电子技术应用,2019,45(9):53-59.

[2]易志强,韩 宾,江 虹,等.基于FPGA 的多通道同步实 时高速数据采集系统设计[J].电子技术应用,2019,45(6)

[3]周楠, 王仁, 覃依漪, 等. 基于异构多核环境下的核间通信机制设计与实现[J]. 计算机工程与设计, 2019, 40(03): 887-893+901.

[4]蒋贵全,张辉,王国锋.基于Linux 的FPGA数据通信接口驱动设计与实现[J].计算机应用,2009,029(009): 2520-2522,2545.

[5]杨磊,刘美枝,高海,等.基于FPGA和ARM的高速数据采集系统的设计[J].山西大同大学学报(自然科学 版),2017,33(6):32-36.

[6]孟庆祥. Linux 教程[M]. 北京:电子工业出版社, 2007.

[7]陆小虎,于东,胡毅,等.基于异构多核处理器的嵌入式数控系统研究[J].中国机械工程,2013(19):2623-2628.

[8]冯瑞青,张激,赵俊才.异构处理器多操作系统协同技术研究[J].计算机系统应用,2018,27(12):90-95.

[9]刘魁,刘健,管增伦,等.基于DSP+FPGA+CPLD 的电 力电子设备通用控制器[J].电子技术应用,2019,45(4):122-126,134.

共0条 [查看全部] 网友评论